Czech Technical University in Prague Faculty of Electrical Engineering Department of Microelectronics

#### PIXEL DETECTOR DESIGNED IN SOI CMOS TECHNOLOGY

Disertation thesis

Ing. Tomáš Benka

Ph.D. programme: P2612 - Electrical Engineering and Information Technology

Branch of study: 2612V015 - Electronics

Supervisor: Doc. Ing. Jiří Jakovenko, Ph.D.

Supervisor specialist: Ing. Miroslav Havránek, Msc., Dr. rer. nat.

#### Thesis Supervisor:

Doc. Ing. Jiří Jakovenko, Ph.D. Department of Microelectronics Faculty of Electrical Engineering Czech Technical University in Prague Technická 2 160 00 Prague 6 Czech Republic

#### Thesis Supervisor specialist:

Ing. Miroslav Havránek, Msc., Dr. rer. nat. Department of Physics Faculty of Nuclear Sciences and Physical Engineering Czech Technical University in Prague Břehová 7 115 19 Prague 1 Czech Republic

Copyright © February 2022 Ing. Tomáš Benka

## Declaration

I hereby declare I have written this doctoral thesis independently and quoted all the sources of information used in accordance with methodological instructions on ethical principles for writing an academic thesis. Moreover, I state that this thesis has neither been submitted nor accepted for any other degree.

In Prague, February 2022

Ing. Tomáš Benka

## Abstract

This work presents development of special class of the Monolithic Active Pixel Sensors (MAPS) sensor which is fabricated in Silicon On Insulator (SOI) CMOS technology. Target application of the sensor is radiation imaging. The deep submicron SOI CMOS technology has long been used in many special applications, such as radiation-hardened or high-voltage integrated circuits.

This disertation thesis deals with the development of a pixel detector with front-end electronics in the deep submicron SOI CMOS technology. The proposed pixel detector is designed and in the 180 nm SOI CMOS commercial technology with the specific process. This study brings the solution to create the prototype of a pixel detector with two different pixel sizes. The first pixel size is 50  $\mu$ m and the second is 100  $\mu$ m. Both pixel types have identical front-end. In the ongoing prototypes, pixel detectors designed in 180 nm SOI CMOS technology have one type of sensor size integrated. The test structures are designed in various sub-microns CMOS technologies as the 180 nm SOI, 180 nm, 150 nm and 65 nm. The prototypes of the integrated circuits design includes test structures for measurement of radiation hardness which is an important criterium of the pixel detectors.

**Keywords:** Pixelated detectors and associated VLSI electronics; X-ray detectors; Frontend electronics for detector readout; Radiation damage to electronic components.

## Abstrakt

Tato práce představuje vývoj speciální třídy MAPS senzoru, který je vyroben v SOI CMOS technologii. Cílovou aplikací senzoru je radiační zobrazování. Hluboká submikronová technologie submicron SOI CMOS se již dlouho používá v mnoha speciálních aplikacích, jako jsou radiačně odolné nebo vysokonapěťové integrované obvody.

Tato disertační práce se zabývá vývojem pixelového detektoru s front-end elektronikou v hluboké submikronové technologii SOI CMOS. Vyvinutý pixelový detektor je navržen v komerční technologii 180 nm SOI CMOS se specifickým procesem. Tato studie přináší řešení pro vytvoření prototypu pixelového detektoru se dvěma různými velikostmi pixelů. Velikost prvního pixelu je 50  $\mu$ m a druhého je 100  $\mu$ m. Oba typy pixelů mají identický front-end. V probíhajících prototypech mají pixelové detektory navržené v technologii 180 nm SOI CMOS integrován jeden typ velikosti pixelu. Testovací struktury jsou navrženy v různých submikrometrových technologiích CMOS jako 180 nm SOI, 180 nm, 150 nm a 65 nm. Prototypy návrhu integrovaných obvodů zahrnují testovací struktury pro měření radiační odolnosti, která je důležitým kritériem pixelových detektorů.

**Keywords:** pixelový detektor, VLSI elektronika; X-ray detektory; Front-end eletronika pro pixelové detektory; radiační poškozemí elektronických komponentů.

## Acknowledgements

I would like to thank my colleagues from the Department of Physics of the FNSPE CTU and also from FEE CTU in Prague, for their patience and valuable expertise they have provided me with. It would not be possible to work on this interesting topic without their great support. I also would like to thank my supervisor doc. Ing. Jiří Jakovenko, Ph.D. and supervisor specialist Ing. Miroslav Havránek, Msc., Dr. rer. nat., who have been consulting various parts of my work, for appreciated advice. Their comments and suggestions helped me to improve my work. I would like to thank to Lukáš Palatinus Dr. rer. nat. from the Institute of Physics of the ASCR for organizing measurement in the Transmission Electron Microscop, Jiří Dluhoš from TESCAN for consultation of the Electron detection measurement, Ing. Vladír Kafka and Ing. Lukáš Tomášek from FSNPE CTU in Prague for their ability and consultations with electrical measurements.

Finally, I would like to thank to prof. Ing. Miroslav Husák, CSc. for admission to Ph.D. studies, my family for their continuous support during the time of my studies and Science 21 foundation for gaining physical and knowledge skills.

## Contents

| act                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\mathbf{iv}$                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| akt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\mathbf{v}$                                                                                                                                                                                   |

| wledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | vi                                                                                                                                                                                             |

| Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ix                                                                                                                                                                                             |

| Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xi                                                                                                                                                                                             |

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\mathbf{x}\mathbf{v}$                                                                                                                                                                         |

| roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                              |

| sertation thesis targets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                                                                                                                              |

| ysicsThe CERN laboratory3.1.1BackgroundPhysics motivation3.2.1Higher and higher energiesThe CERN particle accelerators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6<br>7<br>9<br>10<br>12<br>14                                                                                                                                                                  |

| tel detector in SOI CMOS technology         Background         Developed design         Layout of sensitive elements         Pixel electronics         4.4.1         Charge sensitive amplifier         4.4.2         Discriminator with threshold DAC         4.4.3         Digital logic         Test structures         4.5.1         Amplifier         4.5.2         Transistors for radiation tests         4.5.3         IV characterization and capacitance of sensors         Summary of developed design in 180 nm SOI CMOS technology         Measurement with X-CHIP-02         4.7.1         Transmission electron microscopy imaging | <ol> <li>16</li> <li>17</li> <li>19</li> <li>22</li> <li>23</li> <li>26</li> <li>27</li> <li>29</li> <li>30</li> <li>30</li> <li>31</li> <li>39</li> <li>43</li> <li>45</li> <li>45</li> </ol> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.1.1       Background         Physics motivation                                                                                                                                              |

| <b>5</b>     | Blo                   | cks des | signed in various technologies                                                                 | 53   |

|--------------|-----------------------|---------|------------------------------------------------------------------------------------------------|------|

|              | 5.1                   | Low-V   | Voltage Differential Signaling transmitter / receiver designed in 150                          |      |

|              |                       | nm Cl   | MOS technology                                                                                 | . 54 |

|              | 5.2                   | Summ    | ary of LVDS designed in the 150 nm CMOS technology                                             | . 56 |

|              | 5.3                   | X-CHI   | IP-03                                                                                          | . 57 |

|              |                       | 5.3.1   | Low-Voltage Differential Signaling transmitter / receiver designed<br>in 180 nm SOI technology | . 58 |

|              |                       | 5.3.2   | Summary of X-CHIP-03 LVDS designed in the 180 nm SOI CMOS                                      |      |

|              |                       |         | technology                                                                                     | . 63 |

|              | 5.4                   | LORD    | m S                                                                                            | . 64 |

|              |                       | 5.4.1   | Low-Voltage Differential Signaling transmitter / receiver designed                             |      |

|              |                       |         | in 180 nm SOI technology                                                                       | . 68 |

|              |                       | 5.4.2   | Summary of LORDS LVDS designed in the 180 nm CMOS technolog                                    | y 69 |

|              | 5.5                   | Test st | tructures designed in 65 nm CMOS technology                                                    |      |

|              |                       | 5.5.1   | Voltage DAC                                                                                    | . 71 |

|              |                       | 5.5.2   | Charge injection circuit with voltage DAC                                                      |      |

|              |                       | 5.5.3   | Summary of blocks designed in 65 nm CMOS technology                                            | . 82 |

| 6            | Con                   | clusio  | n                                                                                              | 83   |

|              | 6.1                   | Summ    | ary of thesis                                                                                  | . 85 |

|              | 6.2                   | Fulfilm | nents of targets                                                                               | . 86 |

|              | 6.3                   | Furthe  | er extensibility and recommendations                                                           | . 88 |

| $\mathbf{A}$ | $\operatorname{List}$ | of car  | ndidate's work related to the thesis                                                           | 89   |

|              | List                  | of cand | lidate's work related to the thesis                                                            | . 89 |

| Bi           | bliog                 | graphy  |                                                                                                | 106  |

## List of Acronyms

**AA** Antiproton Accumulator. 15

AC Antiproton Collector. 15

**AD** Antiproton Decelerator. 15

ADC Analog to Dicital Converter. 5, 69

**BI** Beam Intensity. 49, 50

**BOX** Burried-Oxide. 2, 18, 19

CCD Charge-Coupled Device. 2, 52

- **CMOS** Complementary Metal–Oxide–Semiconductor. iv, v, vii, viii, xii–xiv, 1–5, 16–57, 63, 64, 68–71, 82–88

- CSA Charge Sensitive Amplifier. xi, xii, xiv, 22–28, 66, 67, 76, 77

- **DAC** Digital to Analog Converter. vii, viii, xiv, 27–29, 53, 67, 70, 71, 76, 79, 82, 85

- **DNL** Differential NonLinearities. xiv, 5, 71–74, 78, 79, 81, 82, 85

- **DTI** Deep Trench Insulation. xi, xii, 19, 21, 41, 42

- **FPGA** Field Programmable Gate Array. xiii, 55, 56, 61, 62

- **HEP** High Energy Physics. 1

**HV** High Voltage. xii, 19, 24, 25, 39, 41–43, 45, 83, 84

HVP High-Voltage P-well. xii, 31–38, 44

**INL** Integral NonLinearities. xiv, 5, 71–75, 78, 79, 81, 82, 85

**ISR** Intersecting Storage Rings. 9

**LEIR** Low Energy Ion Ring. 14

**LEO** Low Earth Orbit. 5, 64, 87

**LEP** Large Electron-Positron Collider. 9

LHC Large Hadron Collider. xi, 1, 4, 7–10, 13, 14

- **LORDS** Lightweight Orbital Radiation Detection System. viii, xiii, xiv, 5, 53, 61, 63–69, 84, 87, 88

- LSI Large Scale Integration. 17

- LVDS Low-Voltage Differential Signaling. viii, xiii, xiv, 4, 5, 53–64, 68, 69, 84, 86–88

- LVT Low Voltage Threshold. 71, 75, 76

- MAPS Monolithic Active Pixel Sensors. iv, v, 1, 2, 19, 64, 83

- NBUR N-Buried Handle Wafer Diode Module. 22, 24

- NDA Non-Disclosure Agreement. 3

- **OA** Operational Amplifier. 25

- PDH Peak Detector Hold. xiv, 64, 66, 67

- **PS** Proton Synchrotron. xi, 14, 15

- **PSB** Booster rings. 14

- **RHIC** Relativistic Heavy Ion Collider. 10

- **SEE** Single Event Effects. 3, 17, 18

- **SEU** Single Event Upset. 64

- SOI Silicon On Insulator. iv, v, vii, viii, xiii, xiv, 1–5, 16–52, 57–59, 63, 64, 68, 83–88

- SppS Proton-Antiproton Collider. 9, 14

- **SPS** Super Proton Synchrotron. xi, 9, 14, 15

- **STI** Shallow Trench Isolation. 19

- SURE Simple USB Read-out Equipment. xi, 25, 26, 84

- TDAC Digital to Analog Converter for Threshlod adjustment. xi, 23–25, 27, 45

- **TEM** Transmission Electron Microscopy. xii, 4, 43, 46, 47, 52, 84, 87

- TID Total Ionization Dose. 17–19, 31

- VDAC Voltage Digital to Analog Converter. xiv, 5, 70–80, 82, 85

# List of Figures

| 3.1        | In order to explain our everyday world we need two quarks (left). To<br>explain what is happening in our universe we need two more quarks and<br>to explain the formation of our universe [33] as well as certain phenomena                                                                                  | C        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.2        | we need yet another pair of quarks (middle), for a total of six (right) [34]<br>Map of the region close to Geneva where the CERN site is located. The                                                                                                                                                        | 6        |

| 0          | extent of the 27 km Large [40] Hadron Collider is indicated                                                                                                                                                                                                                                                  | 8        |

| 3.3        | The Large Hadron Collider and the experiments Atlas, CMS, LHC-b $\left[42\right]$ .                                                                                                                                                                                                                          | 9        |

| 3.4        | The PS and the SPS accelerator complex [65]                                                                                                                                                                                                                                                                  | 15       |

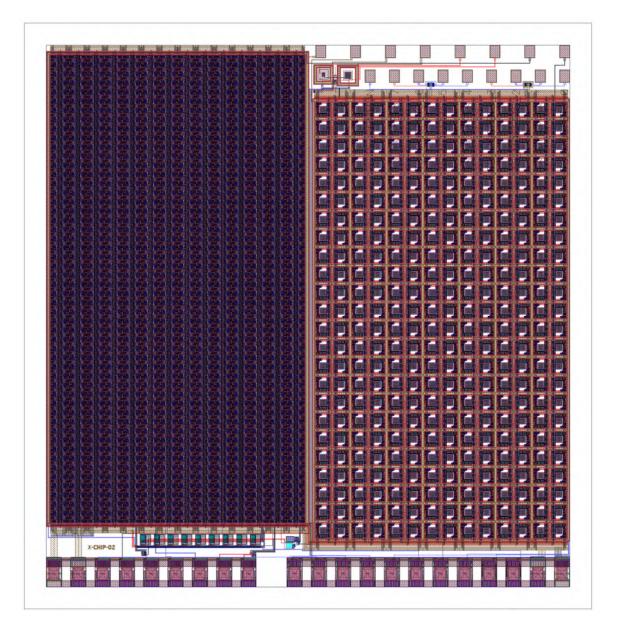

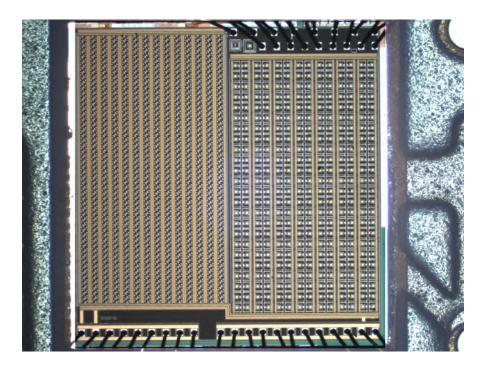

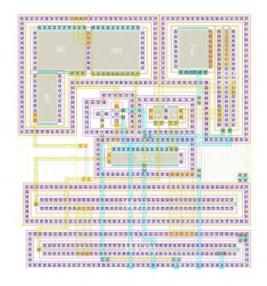

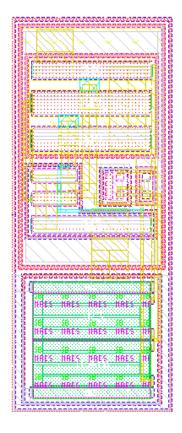

| 4.1<br>4.2 | The layout of X-CHIP-02. The X-CHIP-02 wirebonded on the PCB. On the left side of the chip there                                                                                                                                                                                                             | 20       |

|            | is 50 $\mu$ m pixel pitch matrix with dimensions $2.55 \times 1.4 \text{ mm}^2$ and on the right side there is 100 $\mu$ m pixel pitch matrix with dimensions $2.44 \times 1.4 \text{ mm}^2$ .                                                                                                               | 21       |

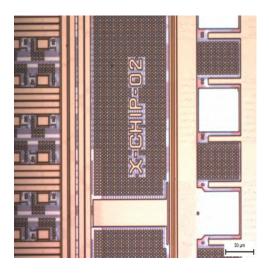

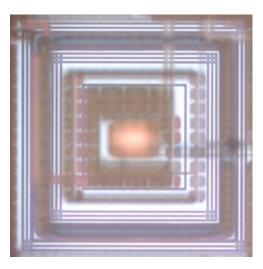

| 4.3        | (Left) The X-CHIP-02 detailed photography. Small objects are fillers to fill the minimum area of the layers. On the right is an open passivation for the wire bonding. The coarse wires crossing the chip represent the power supply in the top metallization. (Right) Detail of the 100 $\mu$ m pixel (test |          |

|            | structure without electronics focused on DTI) [19].                                                                                                                                                                                                                                                          | 21       |

| 4.4        | Layout of the 50 $\mu \mathrm{m}$ pixel. All dimensions are in $\mu \mathrm{m}.$ NMOS and PMOS                                                                                                                                                                                                               |          |

|            | transistors are just for illustration.                                                                                                                                                                                                                                                                       | 22       |

| 4.5        | Layout of the 100 $\mu$ m pixel. All dimensions are in $\mu$ m. NMOS and PMOS                                                                                                                                                                                                                                |          |

| 1.0        | transistors are just for illustration.                                                                                                                                                                                                                                                                       | 23       |

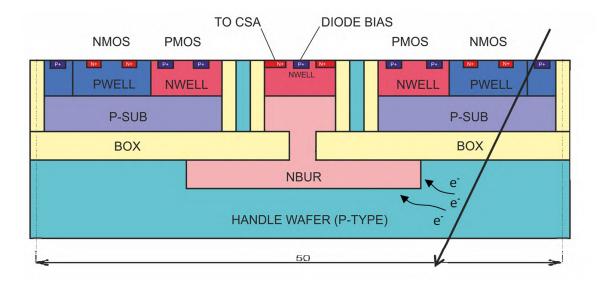

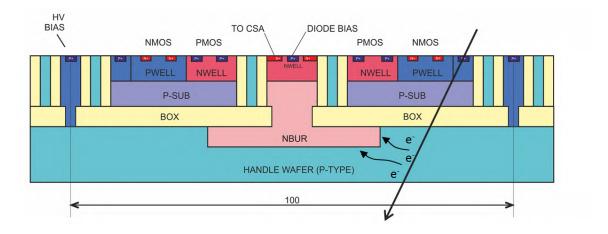

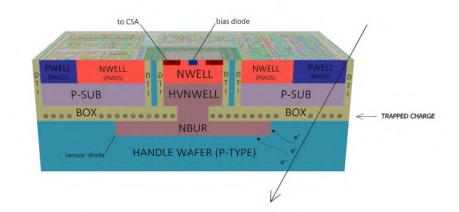

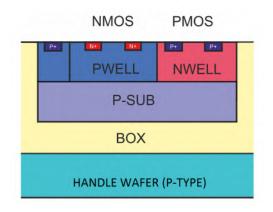

| 4.6        | Cross section and charge collection of X-CHIP-02. The charge collection in POX laws arises during impediation. A high impediation does generated the                                                                                                                                                         |          |

|            | BOX layer arises during irradiation. A high irradiation dose generates the inverse layer of charge in the Handle wafer (SiO–SiO <sub>2</sub> interface) [19]. The                                                                                                                                            |          |

|            | result is a conductive channel. Avoiding this effect can be accomplished                                                                                                                                                                                                                                     |          |

|            | with technology process P-STOP or P-SPRAY, as is described in [81]                                                                                                                                                                                                                                           | 23       |

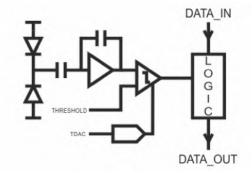

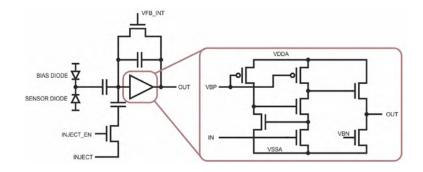

| 4.7        | Block schematic of pixel circuitry of signal processing                                                                                                                                                                                                                                                      | 20<br>24 |

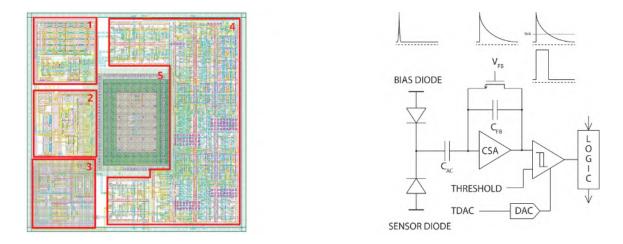

| 4.8        | The X-CHIP-02 pixel electronics. (Left) The 50 $\mu$ m pixel layout: 1 — TDAC,                                                                                                                                                                                                                               |          |

|            | 2 — discriminator, 3 — CSA, 4 — digital logic, 5 — sensitive and bias                                                                                                                                                                                                                                        |          |

|            | diode. (Right) Schematic of the integration pixel [19]                                                                                                                                                                                                                                                       | 24       |

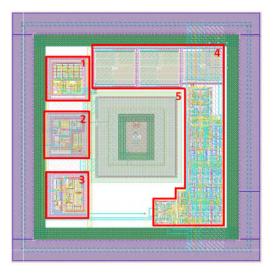

| 4.9        | The 100 $\mu$ m pixel layout, 1 – TDAC, 2 – discriminator, 3 – CSA, 4 – digital                                                                                                                                                                                                                              |          |

|            | logic [19].                                                                                                                                                                                                                                                                                                  | 25       |

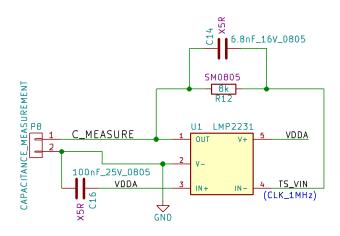

| 4.10       | Circuit for measurement of capacitance of the sensor.                                                                                                                                                                                                                                                        | 25       |

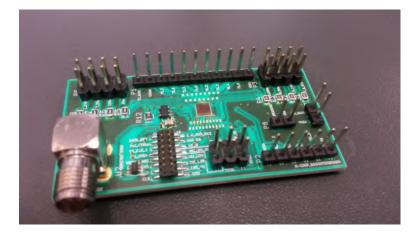

|            | The SURE (motherboard) [19]. $\ldots$                                                                                                                                                                                                                                                                        | 26       |

| 4.12       | The X-CHIP-02-PCB (daughterboard). The X-CHIP-02 is in the middle                                                                                                                                                                                                                                            |          |

|            | of the PCB [19]                                                                                                                                                                                                                                                                                              | 26       |

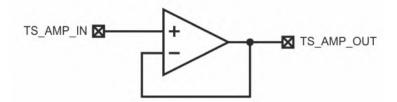

| 4.13       | Schematic of the CSA                                                                                                                                                                                                                                                                                         | 27       |

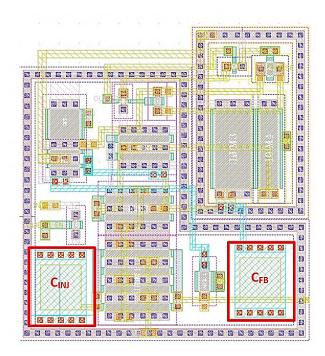

| 4.14 | Layout of the CSA with $C_{INJ}$ and $C_{FB}$                                                     | 27 |

|------|---------------------------------------------------------------------------------------------------|----|

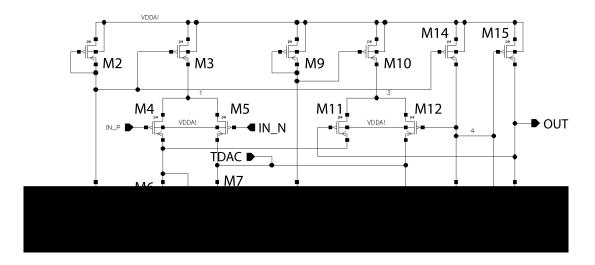

|      | The discriminator with hysteresis and threshold schema.                                           | 28 |

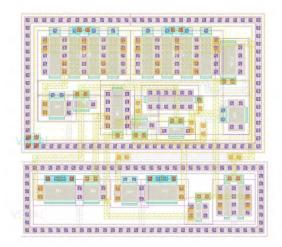

| 4.16 | The discriminator with hysteresis and threshold layout                                            | 28 |

|      | The structure of shift register in X-CHIP-02.                                                     | 29 |

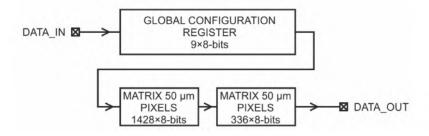

|      | The structure of 50 $\mu$ m and 100 $\mu$ m pixel matrix                                          | 29 |

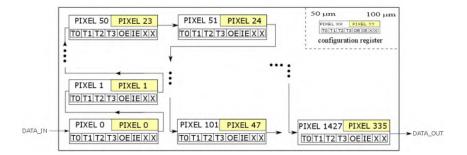

|      | The schematic of stand-alone amplifier                                                            | 30 |

|      | The schematic of the rail to rail analog buffer.                                                  | 31 |

|      | The rail to rail analog buffer layout.                                                            | 31 |

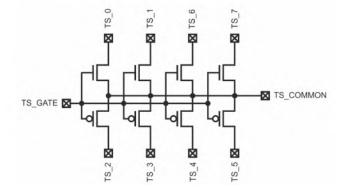

|      | The schematic of transistor for radiation tests.                                                  | 32 |

|      | The layout of the transistor structures with HVP                                                  | 32 |

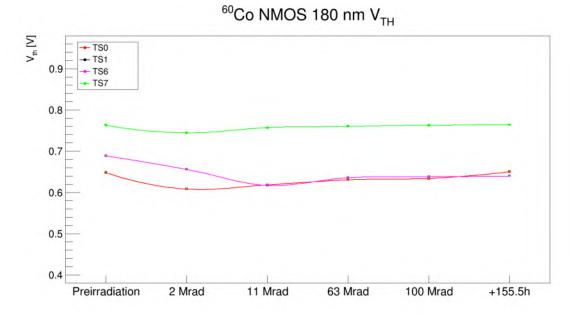

|      | Threshold voltage shifts of the NMOS transistors without / with HVP vs.                           |    |

| 4.05 | <sup>60</sup> Co radiation dose                                                                   | 33 |

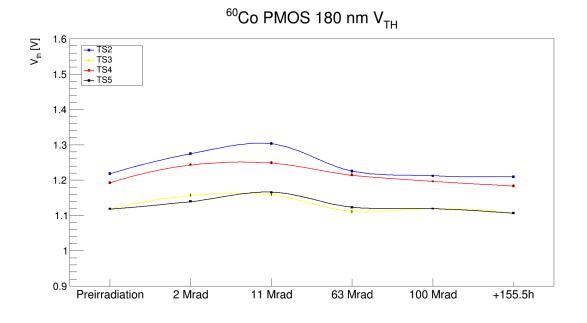

| 4.25 | Threshold voltage shifts of the PMOS transistors without / with HVP vs. $^{60}$ Co radiation dose | 34 |

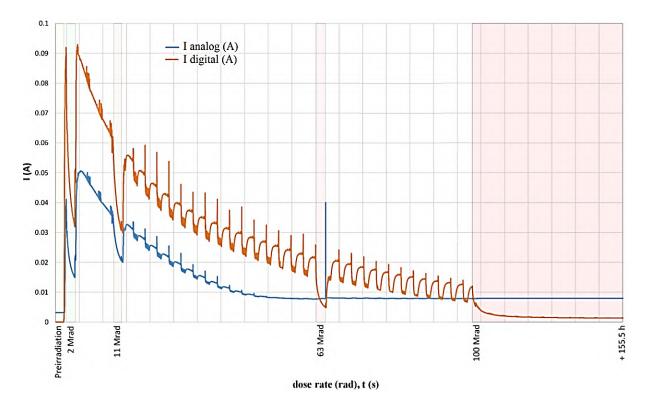

| 4.26 | (Left) the preirradiation area. The analog and digital current of the X-                          |    |

|      | CHIP-02 during irradiation with ${}^{60}$ Co. (Right) is the afteriradiation region at 155.5 h    | 35 |

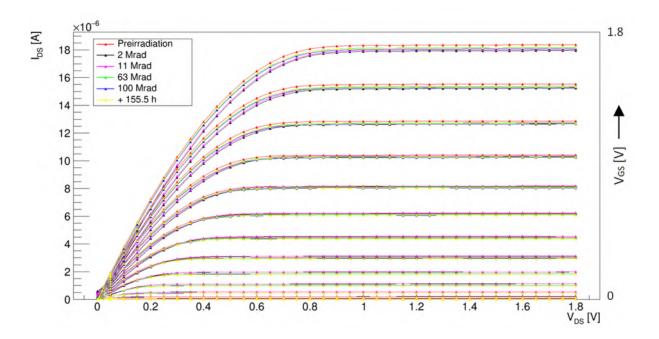

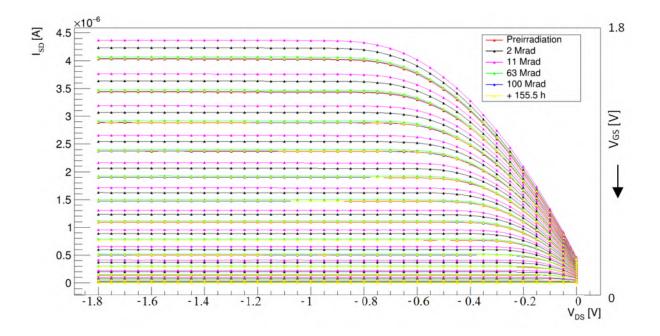

| 4.27 | IV characteristic of TS0 NMOS with HVP structure in 180 nm CMOS                                   |    |

|      | technology for <sup>60</sup> Co radiation dose.                                                   | 35 |

| 4.28 | IV characteristic of TS6 NMOS without HVP structure in 180 nm CMOS                                |    |

|      | technology for <sup>60</sup> Co radiation dose.                                                   | 36 |

| 4.29 | IV characteristic of TS7 NMOS without HVP structure in 180 nm CMOS                                |    |

|      | technology for ${}^{60}$ Co radiation dose.                                                       | 36 |

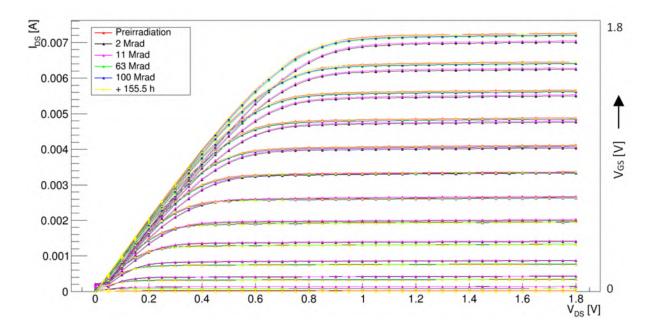

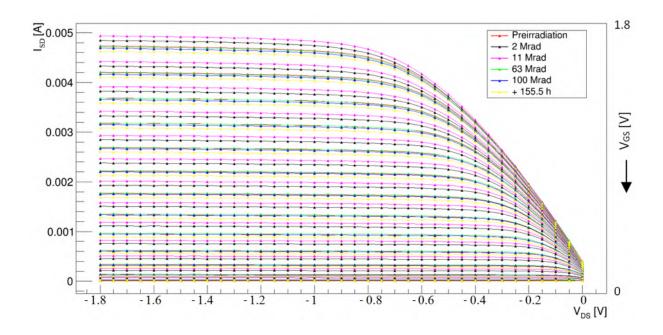

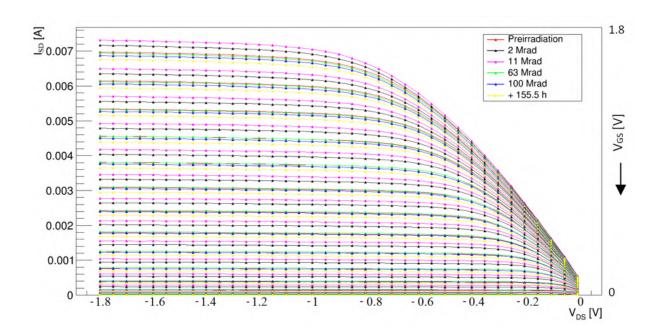

| 4.30 | IV characteristic of TS2 PMOS with HVP structure in 180 nm CMOS                                   |    |

|      | technology for ${}^{60}$ Co radiation dose.                                                       | 37 |

| 4.31 | IV characteristic of TS3 PMOS with HVP structure in 180 nm CMOS                                   |    |

|      | technology for ${}^{60}$ Co radiation dose.                                                       | 37 |

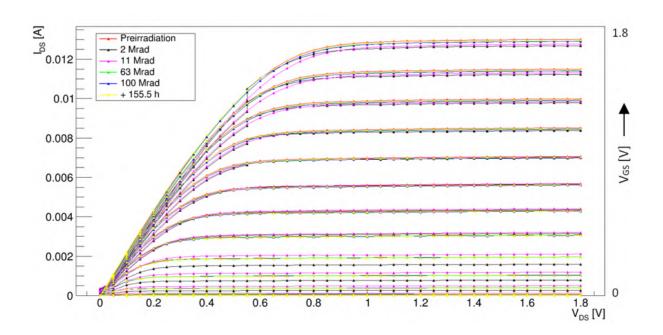

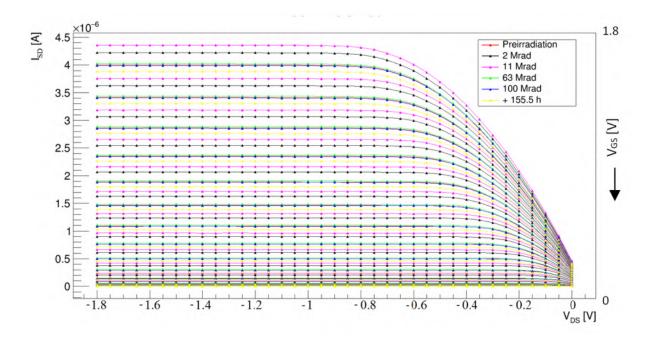

| 4.32 | IV characteristic of TS4 PMOS without HVP structure in 180 nm CMOS                                |    |

|      | technology for ${}^{60}$ Co radiation dose.                                                       | 38 |

| 4.33 | IV characteristic of TS5 PMOS without HVP structure in 180 nm CMOS                                |    |

|      | technology for ${}^{60}$ Co radiation dose.                                                       | 38 |

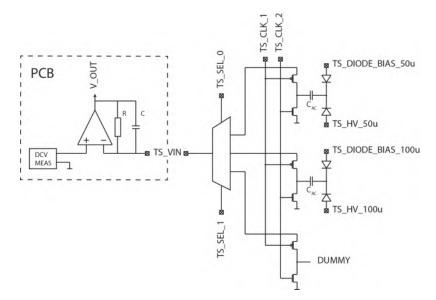

| 4.34 | Schematic of the circuit for measurement of capacitance of the sensor                             | 39 |

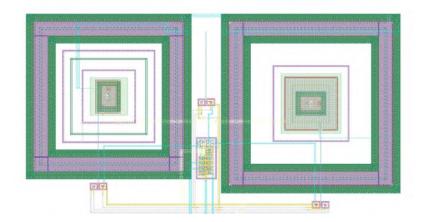

| 4.35 | The test structure of sensor capacitance. (Middle) DUMMY charge pump.                             | 39 |

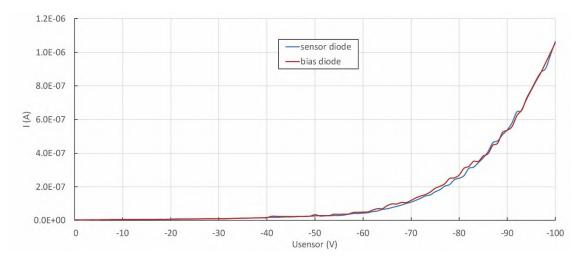

| 4.36 | The IV characteristic of both pixel types in the test structure [19]                              | 40 |

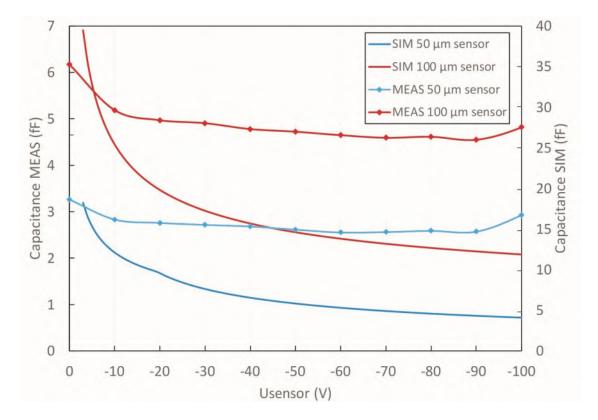

| 4.37 | Electrical measurement (MEAS) and simulation (SIM) of capacitance of                              |    |

|      | the sensor diodes $[19]$ .                                                                        | 41 |

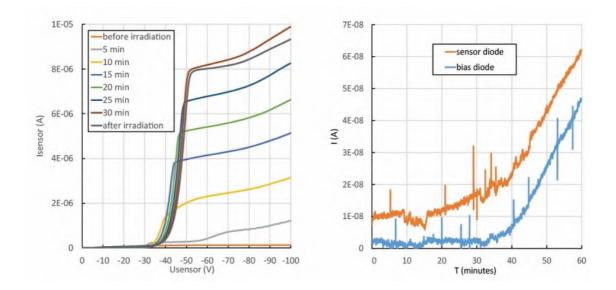

| 4.38 | (Left) IV characteristic during the X-ray irradiation without shielding. The                      |    |

|      | after irradiation curve represents the measurement made 5 minutes after                           |    |

|      | irradiation. (Right) irradiation with lead shielding and a pinhole in the 50                      |    |

|      | $\mu$ m matrix boundary (HV ring — DTI ring) at negative 50 V [19]                                | 42 |

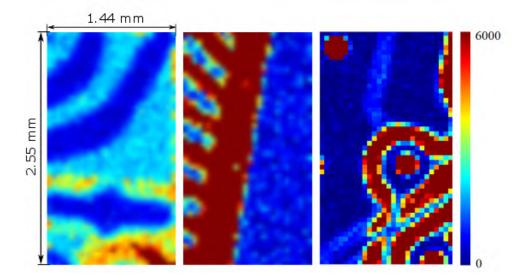

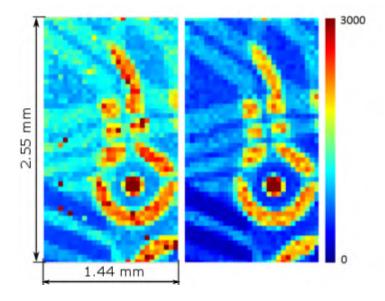

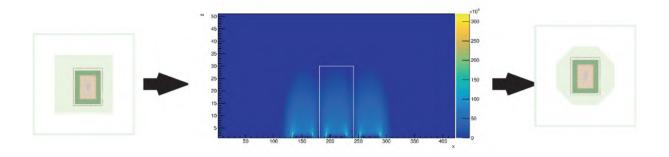

| 4.39 | Imaging structures with X-CHIP-02 (structure on the right is without in-                          |    |

|      | terpolation).                                                                                     | 45 |

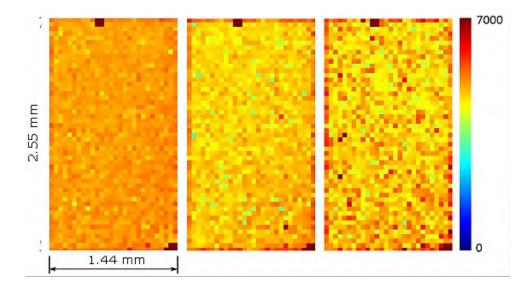

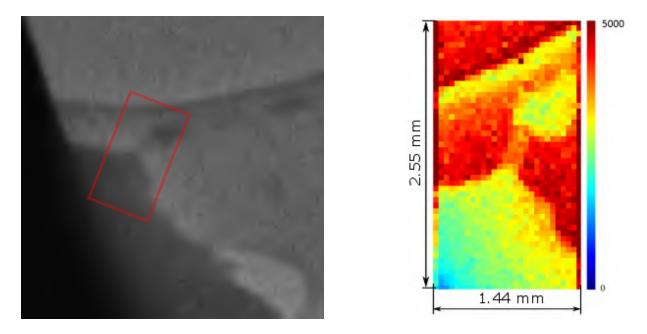

| 4.40 | (Left) the pixels noise equalization of the X-rays, (middle) the pixels noise                     |    |

|      | equalization, (right) without equalization.                                                       | 46 |

| 4.41 | Imaging of the X-rays with and without equalization.                                              | 46 |

|      | (Left) TEM imaging of a carbon foil structures, (e <sup>-</sup> imaging). (Right) The             |    |

|      | X-CHIP-02 imaging in the TEM of a carbon foil structures, (e <sup>-</sup> imaging).               | 47 |

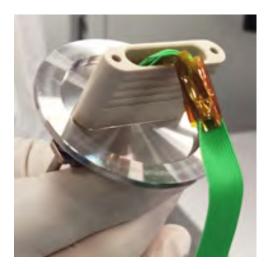

| 4.43         | (Left) the cable connector from the detector. The components of the PCB                                                        |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

|              | and the solder are suitable for vacuum. (Right) the cable is connected via                                                     |     |

|              | a wide reducer to the microscope                                                                                               | 48  |

| 4.44         | (Left) the PCB detector is taped with copper conductive tape and taped                                                         |     |

|              | with Kapton tape. (Right) A foil cover with a hole above the chip                                                              | 48  |

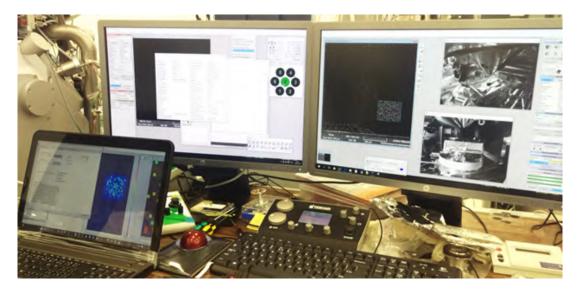

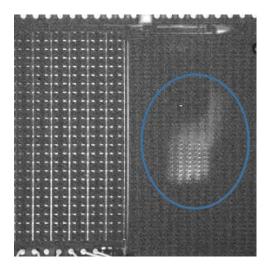

| 4.45         | Observation of images during measurement. The area where the beam was                                                          |     |

|              | rasterized at the highest possible speed $(10 = 0.1 \ \mu s \ / pxl)$ can be seen on                                           |     |

|              | the PC monitor. The corresponding rectangular area on the direct detector                                                      |     |

|              | is visible on the notebook.                                                                                                    | 49  |

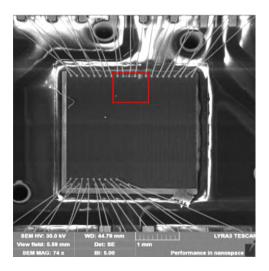

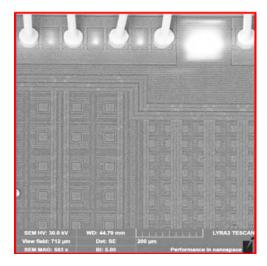

| 4.46         | (Left) A picture of the whole chip with wirebonds. (Right) a detail of a                                                       |     |

|              | chip with 100 $\mu$ m and 50 $\mu$ m pixels                                                                                    | 49  |

| 4.47         | (Left) in the ring is the irradiated area after several minutes of irradia-                                                    |     |

|              | tion. (Right)The picture of the chip from the second day the chip was                                                          |     |

|              | disconnected overnight.                                                                                                        | 50  |

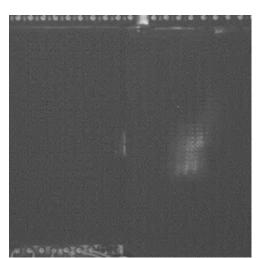

| 4.48         | (Left) A picture of the chip is taken a few minutes after plugging. (Right)                                                    |     |

|              | detailed picture of metallization charging.                                                                                    | 51  |

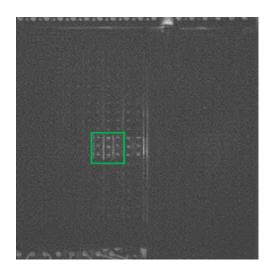

| 4.49         | On the photos is plotting the beam in lines to measure the detector's effi-                                                    |     |

|              | ciency, which is further measured depending on the amount of bias                                                              | 51  |

|              |                                                                                                                                |     |

| 5.1          | The LVDS transmitter in 150 nm CMOS technology.                                                                                | 54  |

| 5.2          | The LVDS receiver with output invertor in 150 nm CMOS technology, R1                                                           |     |

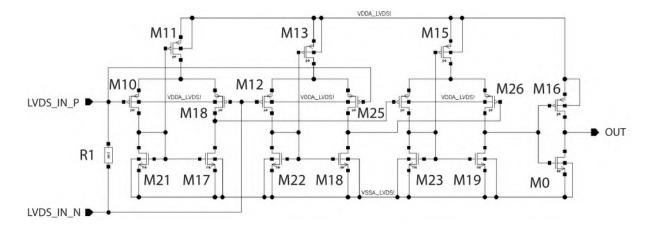

| <b>F</b> 0   | $= 100 \ \Omega. \dots $ | 55  |

| 5.3          | The LVDS receiver with output invertor in 150 nm CMOS technology, R1                                                           |     |

| <b>_</b> ,   | $= 100 \ \Omega. \dots $ | 55  |

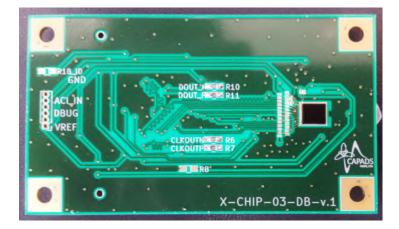

| 5.4          | The CHIP-03 PCB dagther board with respect to lines impedance                                                                  | 57  |

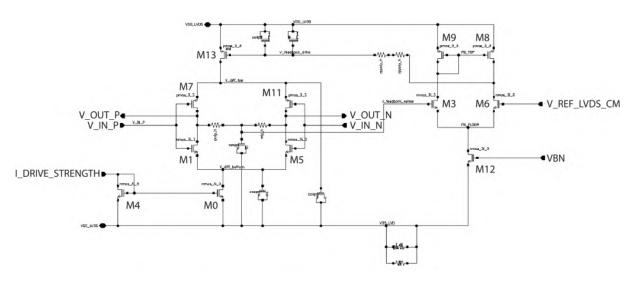

| 5.5          | The CHIP-03 LVDS transmitter schema with adjustable current strenght                                                           | -   |

| -            | designed in 180 nm SOI technology                                                                                              | 58  |

| 5.6          | The CHIP-03 LVDS transmitter layout in 180 nm SOI technology                                                                   | 59  |

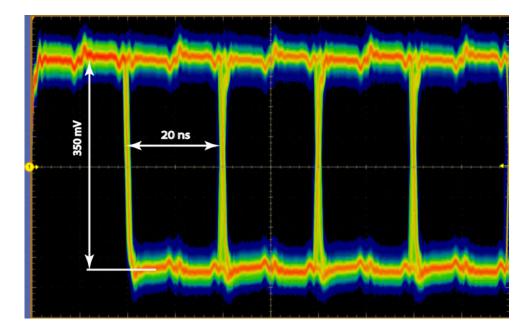

| 5.7          | The electrical measurement of the CHIP-03 LVDS driver at 50 MHz and                                                            |     |

| <b>F</b> 0   | LVDS_STRENGTH 110. The common mode voltage is 350 mV at 50 mV/div.                                                             | 60  |

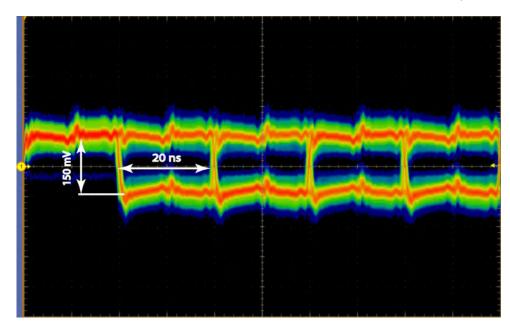

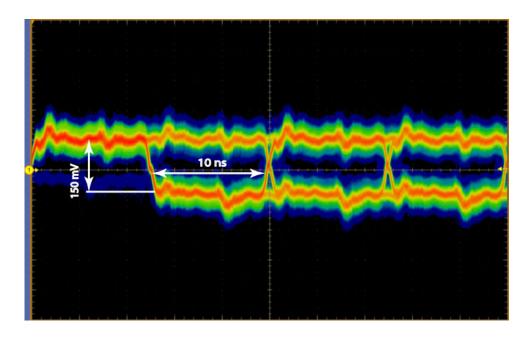

| 5.8          | The electrical measurement of the CHIP-03 LVDS driver at 50 MHz and                                                            |     |

| 50           | LVDS_STRENGTH 170. The common mode voltage is 150 mV at 50 mV/div.                                                             | 60  |

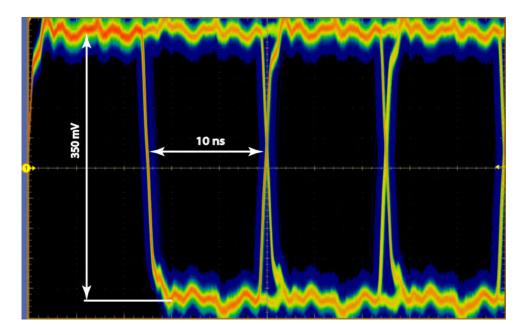

| 5.9          | The electrical measurement of the CHIP-03 LVDS driver at 100 MHz and                                                           | 01  |

| <b>F</b> 10  | LVDS_STRENGTH 110. The common mode voltage is 350 mV at 50 mV/div.                                                             | 61  |

| 5.10         | The electrical measurement of the CHIP-03 LVDS driver at 100 MHz and                                                           |     |

| <b>F</b> 1 1 | LVDS_STRENGTH 170. The common mode voltage is 150 mV at 50 mV/div.                                                             | 62  |

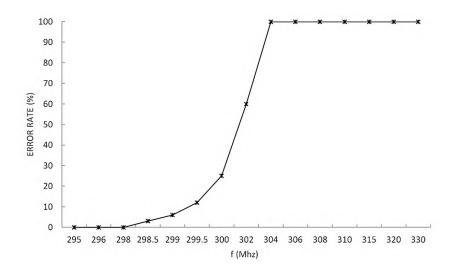

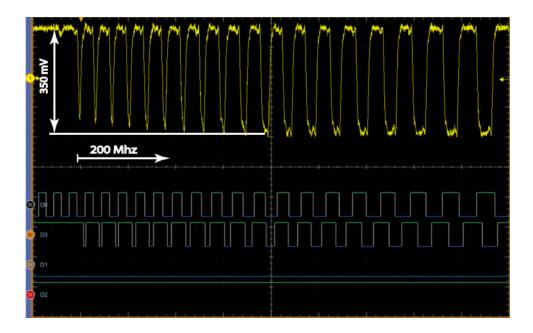

| 5.11         | The electrical measurement of the CHIP-03 LVDS driver at frequency drop                                                        |     |

|              | from 200 MHz and LVDS_STRENGTH 110, 200 mV/div. The yellow and                                                                 |     |

|              | third curve (D3) is the output of the LVDS transmitter, second curve (D0)                                                      |     |

| <b>F</b> 10  | is the clock output from the FPGA and the input for the LVDS receiver.                                                         | 62  |

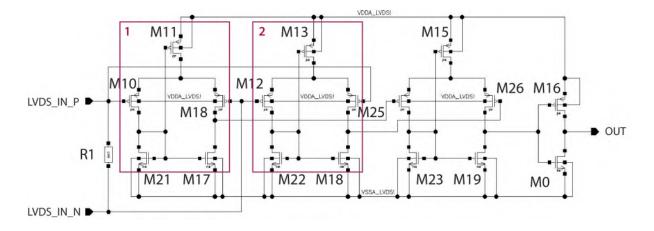

| 5.12         | The LVDS receiver design of the X-CHIP-03, the red boxes are the input                                                         | 0.5 |

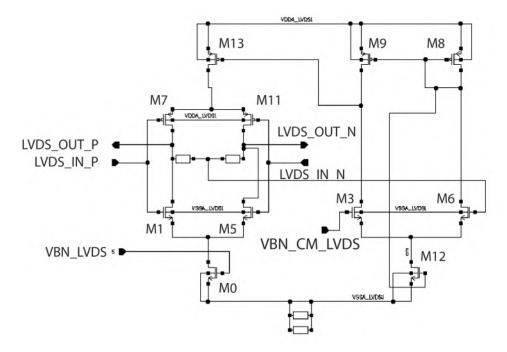

| <b>F</b> 4 0 | stages of the receiver                                                                                                         | 63  |

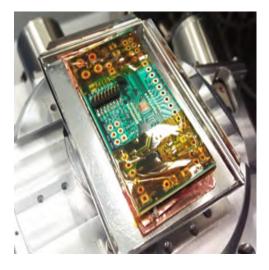

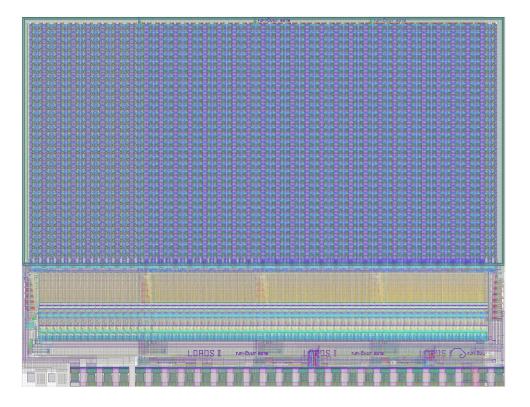

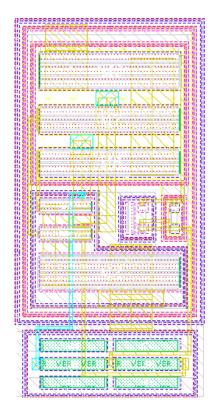

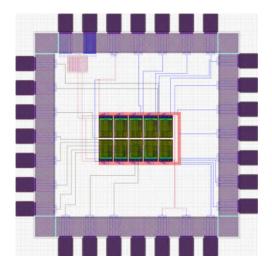

|              | The layout of the LORDS.                                                                                                       | 65  |

|              | The LORDS communication architecture.                                                                                          | 65  |

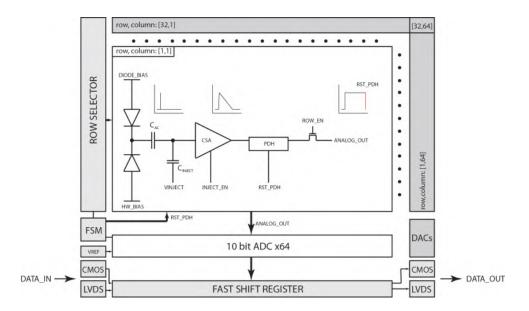

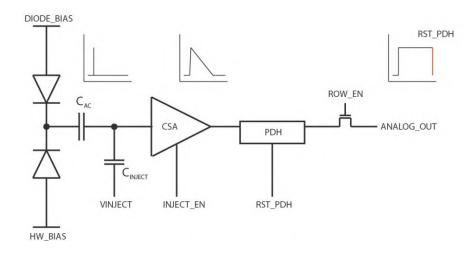

| 5.15         | The pixel block diagram of the LORDS.                                                                                          | 66  |

| 5.16  | (Left) the standard sensor design in the X-CHIP-02 and X-CHIP-03. (Mid-<br>dle) the density of the electric field with the standard sensor design, three<br>pixels with 50 $\mu$ m pixel size. (Right) the octogonal sensor design in the LORDS |          |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                           | 66       |

| 5.17  | The simulation of the LORDS pixel electronics. The first curvers are                                                                                                                                                                            |          |

|       | the CSA output from 2400 $e^-$ to 300 000 $e^-$ and the second is the PDH output for the DAC input                                                                                                                                              | 67       |

| 5 1 9 | output for the DAC input                                                                                                                                                                                                                        | 68       |

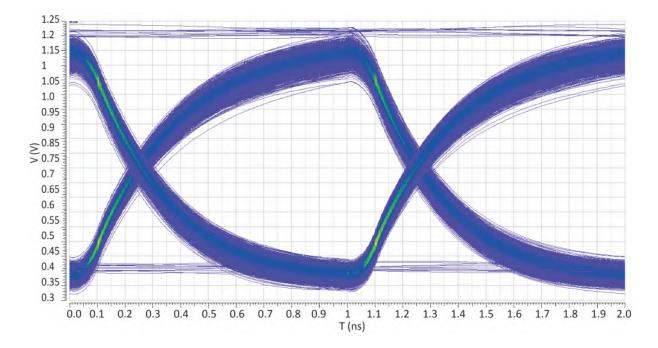

|       | The LORDS EVDS transmitter layout in 180 nm SOI technology The LORDS eye diagram of the differential signal at 0.5 Gbps                                                                                                                         | 08<br>69 |

|       | The first prototype of the VDAC layout designed in 65 nm CMOS tech-                                                                                                                                                                             | 09       |

| 5.20  | nology. Inside the chips are 10 DACs for the voltage dispersion measurement.                                                                                                                                                                    | 71       |

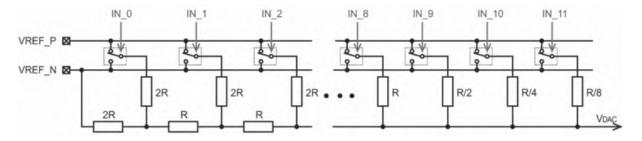

| 5 91  | The DAC structure 10-bit R-2R with 4-bit weighted ladder.                                                                                                                                                                                       | 71<br>71 |

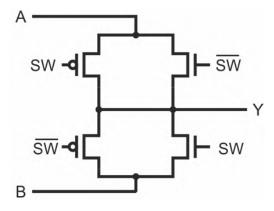

|       | The switch schema of the the VDAC.                                                                                                                                                                                                              | 71<br>72 |

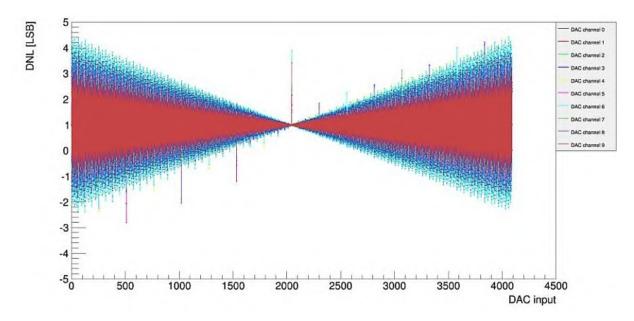

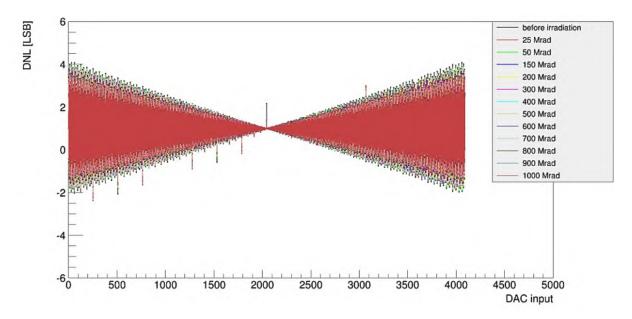

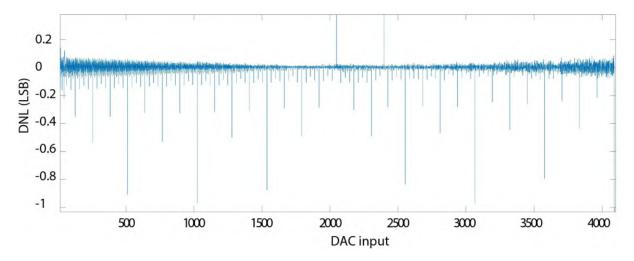

|       | The DNL electrical measurement of the first prototype of the VDAC.                                                                                                                                                                              | 72<br>72 |

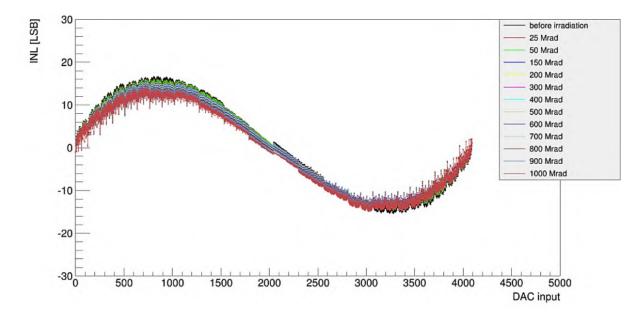

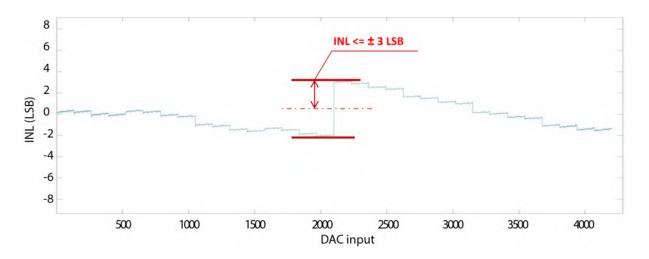

|       | The INL electrical measurement of the first prototype of the VDAC                                                                                                                                                                               | 73       |

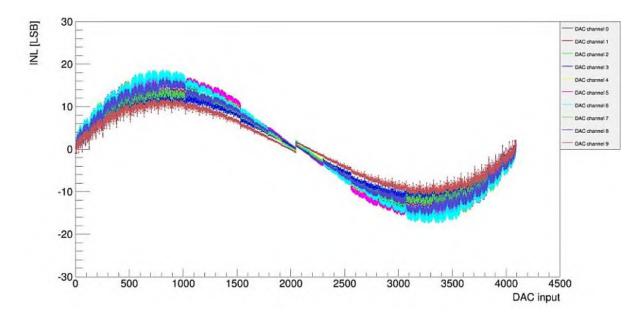

|       | The DNL irradiation measurement of the first prototype of the $^{60}$ Co                                                                                                                                                                        | 73       |

|       | The INL irradiation measurement of the first prototype with ${}^{60}$ Co                                                                                                                                                                        | 73<br>74 |

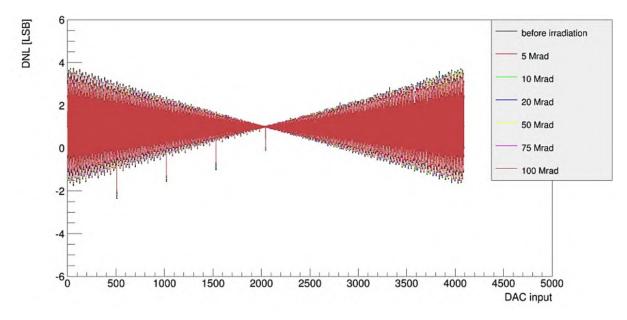

|       | The DNL irradiation measurement of the first prototype with X-rays                                                                                                                                                                              | 74       |

|       | The INL irradiation measurement of the first prototype with X-rays                                                                                                                                                                              | 74       |

|       | The layout of the INJECT_CHIP.                                                                                                                                                                                                                  | 76       |

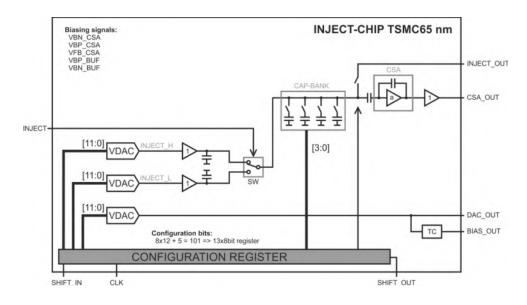

|       | The block scheme of the INJECT_CHIP.                                                                                                                                                                                                            | 77       |

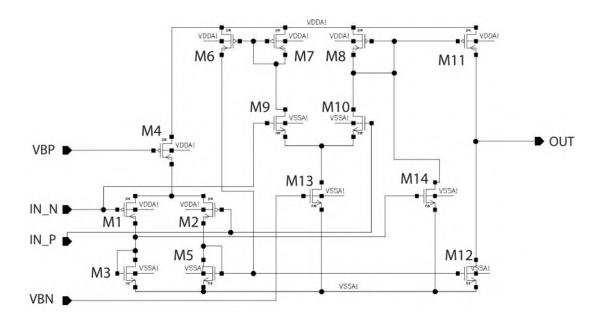

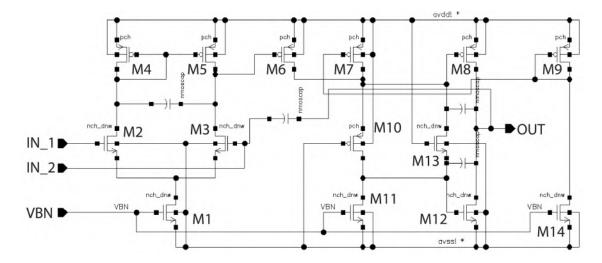

|       | The scheme of the voltage buffer (AMP_H) of the INJECT_CHIP.                                                                                                                                                                                    | 77       |

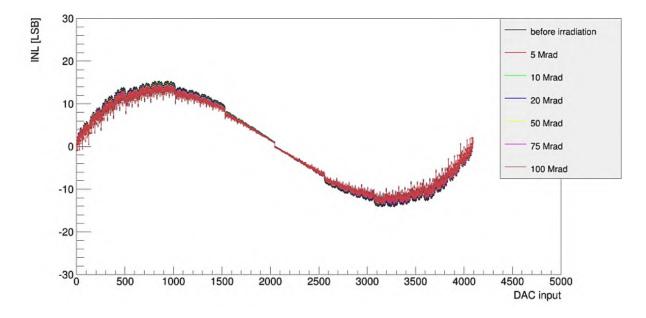

|       | The DNL electrical measurement of the second prototype the INJECT_CHIP                                                                                                                                                                          | • •      |

| 0.02  | VDAC.                                                                                                                                                                                                                                           | 78       |

| 5 33  | The INL electrical measurement of the second prototype the INJECT_CHIP                                                                                                                                                                          | 10       |

| 0.00  | VDAC.                                                                                                                                                                                                                                           | 78       |

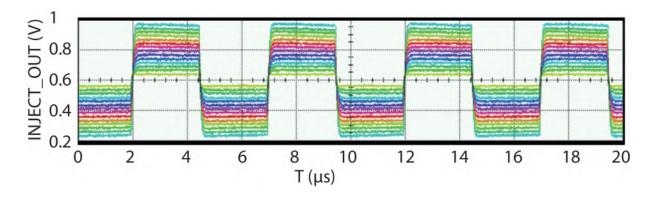

| 5.34  | The electrical measurement of the INJECT_CHIP. The measured output is                                                                                                                                                                           | •0       |

| 0.01  | the INJECT_OUT; INJECT = $200 \text{ kHz} @ 2 \text{ pF}. \dots \dots \dots \dots \dots \dots$                                                                                                                                                  | 79       |

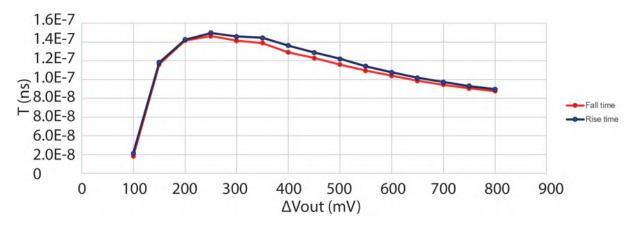

| 5.35  | The rise and fall time of the INJECT_OUT of the INJECT_CHIP at IN-                                                                                                                                                                              | 10       |

| 0.00  | JECT = 200  kHz @ 2  pF.                                                                                                                                                                                                                        | 79       |

| 5.36  | The electrical measurement of the INJECT_CHIP. The measured output                                                                                                                                                                              |          |

|       | is the CSA_OUT; Voltage Digital to Analog Converters (VDACs) inject is                                                                                                                                                                          |          |

|       | from 100 mV to 700 mV with 50 mV step. The smallest curve corresponds                                                                                                                                                                           |          |

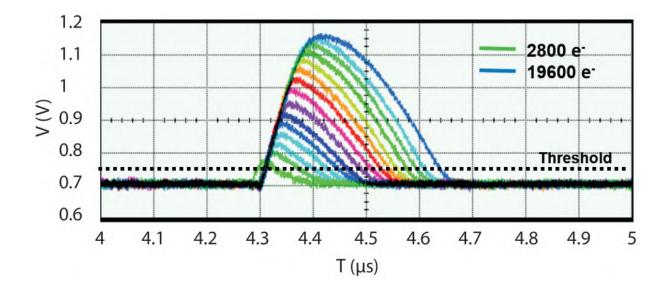

|       | to $2800 e^-$ and the highest to $19.600 e^-$ .                                                                                                                                                                                                 | 80       |

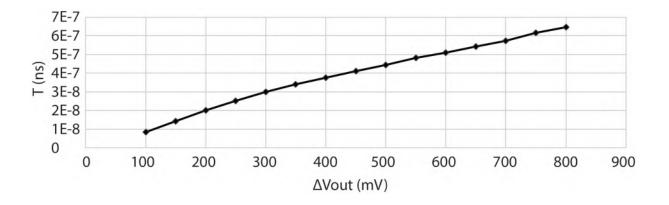

| 5.37  | Characterization the time over threshold of the Charge sensitive amplifier;                                                                                                                                                                     |          |

|       | CSA_OUT; the threshold of the pulse length measurement is $50 \text{ mV}$ (TOT).                                                                                                                                                                | 80       |

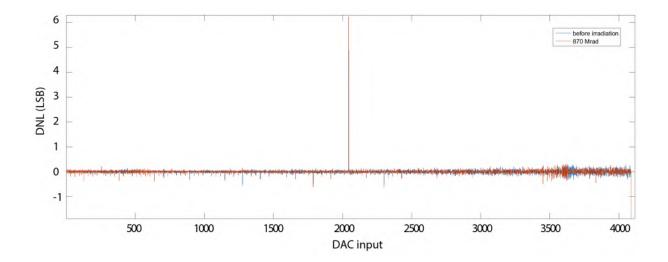

| 5.38  | The DNL irradiation measurement of the second prototype INJECT_CHIP                                                                                                                                                                             |          |

|       | with X-rays up to 870 Mrad                                                                                                                                                                                                                      | 81       |

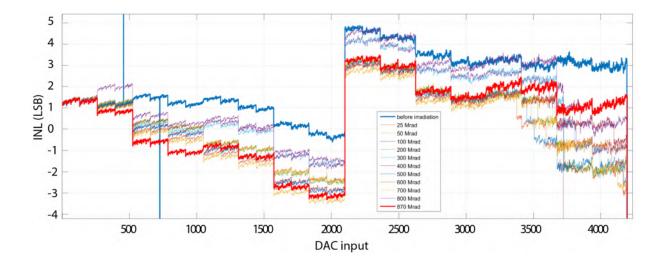

| 5.39  | The INL irradiation measurement of the second prototype INJECT_CHIP                                                                                                                                                                             |          |

|       | with X-rays up to 870 Mrad                                                                                                                                                                                                                      | 81       |

# List of Tables

| 3.1 | Fermions: leptons and quarks [35].     | • | 11 |

|-----|----------------------------------------|---|----|

| 4.1 | Description of MOSFET test structures. |   | 33 |

# Chapter 1

## Introduction

Currently, it is difficult to find a pixel detector of ionizing radiation with the corresponding parameters at an affordable price. The selection of suitable technology is governed mainly by price per  $mm^2$  of the proposed chip and technology difficulty. One of the most widespread detectors is hybrid pixel detector technology, as is described in [1], which has sufficient parameters, but it is constructed in a very complex technology – higher price. Hybrid pixel detectors are popular in High Energy Physics (HEP) experiments for tracking and vertexing. Vertex detectors using this technology have been successfully implemented in experiments at the Large Hadron Collider (LHC): ATLAS [2], CMS [3] and ALICE [4]. Hybrid pixel detectors are distinguished by their excellent spatial resolution, low noise, radiation hardness, fast read-out and small inserted mass in the detector. A hybrid pixel detector is a composition of sensor and read-out chip interconnected by a suitable technology [5]–[7]. Lower limit of the pixel size restricts the technology to bumpbonding. This approach allows an independent development of these components and more freedom in design and fabrication. On the other hand, the interconnection process represents a significant portion of a financial budged for the detector production. The main leader in applications of the hybrid pixel detectors is the Medipix collaboration at CERN. The Medipix hybrid pixel detector can be combined with different semiconductor sensors which convert the ionizing radiation directly into detectable electric signal [8], [9]. Recently, more advanced technologies became available. The integration of a sensor and the complex Complementary Metal–Oxide–Semiconductor (CMOS) front-end electronics on the same chip becomes possible. The sensor and the front-end electronics are integrated on one piece of silicon. In this detector group are included the MAPS and detectors fabricated in SOI CMOS technology.

The MAPS is an integration of a sensor and front-end electronics on the same silicon wafer, thus overcoming the interconnection issues. An additional advantage of this solution is the possibility to design small pixels with small capacitance and potentially low noise. The MAPS can be thinned down to a thickness of several tens of  $\mu$ m. A thin sensor with fine pixel granularity is demanded in the future HEP experiments, for example at the future linear collider CLIC [10] or ILC [11]. The sensor requires pure, high resistivity silicon (several k $\Omega$ ) and high depletion voltage, while CMOS electronics is usually processed on low resistivity (< 10  $\Omega$ .cm) silicon and biased with low voltage (< 2 V). The technologies adopting the desired features have not been widely available until the last decade. Nowadays, many commercial applications require technologies meeting the requirements for fabrication of the MAPS sensors. The CMOS image sensors are a typical example. In recent years, the market of the CMOS image sensors started to grow largely due to their massive integration in mobile devices. The sales of the CMOS image sensors are currently higher than the Charge-Coupled Device (CCD) [12]–[14].

This work presents development of special class of the MAPS sensor which is fabricated in SOI CMOS technology. Target application of the sensor is radiation imaging. The deep submicron SOI CMOS technology has long been used in many special applications, such as radiation-hardened or high-voltage integrated circuits. It is only in recent years that SOI has emerged as a serious contender for low-power high-performance applications [15]–[18]. The main feature of the SOI pixel detectors is the sensor location. A sensor element is implemented on handling wafer. The epitaxial layer which contains the front-end electronics is separated from the sensitive part of Burried-Oxide (BOX), a detailed description is in [19] by T. Benka and in [20]–[22]. This technology has a huge advantage in separating the front-end electronics from the sensor part while maintaining both at the same chip. The SOI CMOS technology has favorable price per mm<sup>2</sup>, availability of technology in factories, competitiveness for other technologies – chiefly for pixel hybrid detectors.

## Chapter 2

## **Dissertation thesis targets**

For a long time, the performance of the MAPS sensors has been limited due to the absence of suitable technologies allowing the integration of a sensor and the complex deep submicron CMOS electronics on the same chip is a technological challenge. Microelectronic circuits manufactured using silicon transistors fabricated on an insulating substrate (SOI) are often used in high reliability system designs. The SOI technologies continue to be developed and applied to address radiation requirements of future generation pixel detectors in various industries. The intrinsically limited collection volume of an SOI device can reduce the impact of Single Event Effects (SEE) and transient dose radiation. The case has been made that soft error mitigation may be a motivating factor for more widespread commercial adoption of the SOI, and the commercial SOI devices to below 180 nm. Lower voltages, thinner silicon and the BOX layers, new materials in devices and over layers, and non-planar multiple gate device structures have implications for radiation effect in the SOI devices. Shorter channel lengths increase the parasitic bipolar gain, know to enhance the SEE and transient dose vulnerability in advanced SOI. Thinner BOX layers can exacerbate capacitive coupling from charge deposited in the substrate. The Modern digital SOI circuits may even be sensitive to energetic protons or electrons. With thinning of the silicon layer, the total-ionizing-dose radiation response of the BOX layer and associated interfaces, in closer proximity to the devices channel(s) becomes of increased relevance. The number of the international experimets uncontrollably rises which require the solutions in the SOI CMOS technologies. The major experiments at the international organizations CERN are: ATLAS [2], CMS [3], CLIC [10] and many others. The completed functional solutions are designed in smaller collaborations, such as the Departments of the Universities. Research result obtained with the novel MAPS detectors are often published and they are avalable to academic community. Design details (schematics with transistor dimensions) are often kept secret within the research group. Technology details are Non-Disclosure Agreement (NDA) protected or not avalable to academic community at all. It is therefore understanbadle, that certain sensitive information can not be presented in this document. For the development of the pixel detector, the submicron 180 nm SOI CMOS technology has been chosen. The SOI CMOS technology allows the production with the specific process the sensor part which is located under the front-end electronics, T. Benka [19], [23]–[25]. Target application of the presented detector is X-ray imaging. Other applications of the detector are particle identification and measure the spectrum of different particles (ions, electrons and soft photons [26]). Some of these applications have been described by Z. Janoska, T. Benka et al in [27]. Nowadays, many commercial applications require technologies, which correspond the requirements for fabrication of the MAPS sensors. It may lead to new types of particle imaging detectors, for example, the upgrade of the LHC experiment, imaging detectors in medicine described by G. Neue, T. Benka et al in [28], detectors for dosimetry, G. Neue, T. Benka et al., etc. in [29]–[32]. The main advantage compared to hybrid pixel detectors is integration of sensor and front-end electronics on the same silicon chip.

The presented dissertation study was created to show the current state of research which is represented by the imaging pixels detector X-CHIP-02. Specifically, this study focuses on the development of the pixel detector X-CHIP-02 which is manufactured in ultra-deep submicron 180 nm SOI CMOS technology. Basic parameters and important blocks of the X-CHIP-02, as well as the latest results, are described. Knowledge and experience with pixel detectors were obtained during solving the research project and grants that were solved at the Department of Microelectronics FEE CTU and at the Department of Physics FNSPE CTU in Prague. The proposals of the chip have been developed in cooperation with Advanced Detection Systems of Ionizing Radiation Project at the FNSPE CTU in Prague. All the relevant circuit blocks of pixels detector X-CHIP-02, tests structures and other prototypes of micloelectronics circuits and datectors designed in 180 nm SOI, 180 nm, 150 nm and 65 nm CMOS technology are presented in this dissertation. The main objectives of this work are in the following reflections:

- Design, implementation and electrical measurement of the X-CHIP-02 pixels detector 180 nm SOI CMOS technology. Functionality verification of the X-CHIP-02 with the TEM, <sup>60</sup>Co and X-rays, characterization of the test structure of the X-CHIP-02 during irradiation.

- Description of individual processes of radiation resistance of developed structures in 180 nm SOI CMOS technology.

- Development of the second prototype of the X-CHIP-02 pixel detector in 180 nm SOI CMOS technology the X-CHIP-03 and LVDS drivers for the communications.

- Characterization of the LVDS drivers with electrical measurement. Evaluation of the necessary modifications for the next version of the microelectronic structure for the required communication speed.

- Development of the thirds prototype of the X-CHIP-02 pixel detector in 180 nm SOI CMOS technology the LORDS octagonal pixels detector for Low Earth Orbit (LEO) with required parameters of this detector for the purpose of its use LVDS drivers modification for the large - scale detectors. The electrical measurements of the pixel electronics and its radiation tolerance.

- The verification of the LVDS drivers, Development the detector with Analog to Dicital Converter (ADC) mode and implementing a voltage density improvement in the sensor (handle wafer) by an octagonal sensor design.

- Development, implementation, electrical measurement and radiation tests at 1000 Mrad in the 65 nm CMOS technology the voltage Digital-to-analog converter with the appropriate circuits to perform the radiation tests.

- The verification of radiation resistance at 1000 Mrad of the microelectronics structures designed in 65 nm CMOS technology from various sources as <sup>60</sup>Co and X-rays. The first and second prototypes characterization during irradiation of the VDAC and definition of the INLs and DNLs according to requirements.

## Chapter 3

## Physics

The nature of our universe has always intrigued man. The exploration of what we are, why we are, and where we are has been objects of considerable effort since the beginning of our existence see Figure 3.1. Today, constructing and exploiting the tools needed to continue this exploration require extensive collaboration efforts in both economic and intellectual terms. The CERN laboratory is a fruit of a successful collaboration in Europe, now housing many different particle accelerators of varying sizes used to explore physics. Other non-European countries have joined CERN and its many physicists as partners to share this quest for new knowledge.

Figure 3.1: In order to explain our everyday world we need two quarks (left). To explain what is happening in our universe we need two more quarks and to explain the formation of our universe [33] as well as certain phenomena we need yet another pair of quarks (middle), for a total of six (right) [34].

Particle accelerators can accelerate different kinds of particles such as electrons, positrons, protons, antiprotons and ions. The accelerated particles are formed into beams which can be guided using magnetic or electrical fields to strike and to interact with the target material or made to collide and interact with other accelerated particles. By studying the results of these interactions our knowledge about matter is successively improved. Increasing the energy of the accelerated particles provides us with a better tool to probe the structure of the particles making up matter and their interactions. An increase of the

particle energy results in an increase of the power of resolution of our observation, which in turn brings us closer to the conditions that existed in our universe at its "birth". This increase in particle energy has a price: either the magnets providing the guiding field are made stronger to contain the particles in the machine or the radius of the accelerator is enlarged [35].

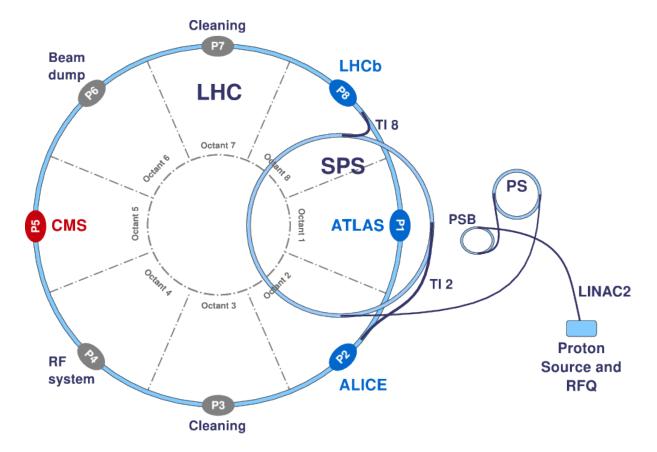

The LHC machine, now being assembled at CERN [36], actually uses both options. The magnetic field used in the main bending dipole magnet is an unprecedented 8.35 T and the circumference of the machine is a huge 27 km. The LHC machine is the last link in a chain of CERN accelerators that are required to permit the acceleration of protons from rest energy to 7 TeV, and important upgrades of all these machines have been made [Ben05] to enable the best possible performance. Many issues related to diagnostics are of vital importance for the technologically very challenging scientific instrument which is the LHC. Particle accelerators are equipped with extensive diagnostic tools and real-time controls. Automatic beam steering, beam tuning and detailed knowledge of the properties of the superconducting magnets, some of the subjects treated in this work, are major issues when trying to reach 7 TeV.

#### 3.1 The CERN laboratory

CERN, the European Organization for Nuclear Research, is the world's leading laboratory for particle physics. Its mission is fundamental physics – exploring the fundamental constituents of matter and what the universe is made of. The main tool for research is the Organization's unique network of particle accelerators, which collide beams of particles or direct them to fixed-target experiments. Giant detectors record the results of these collisions, providing data to thousands of physicists from all over the world for analysis.

Founded in 1954, CERN is an intergovernmental organisation headquartered in Meyrin, in the Canton of Geneva, Switzerland (Figure 3.2). It is governed by its 23 Member States. It also brings together eight Associate Member States and six Observers. It has become a prime example of international collaboration, uniting people from all over the world to push the frontiers of science and technology for the benefit of all. The history of CERN is described for example in [35]–[38].

CERN has two main campuses, the original Meyrin site on the French/Swiss border, and the Prévessin site in France. There are also smaller sites around the 27-kilometre ring of the LHC, situated in both countries. These are host to unprecedented experiments resulting from worldwide collaborations between nations, universities, and scientists.

Over 17 900 people from around the world work together on CERN-based projects, constantly advancing the limits of knowledge. Around 3600 of them are employed by

#### CHAPTER 3. PHYSICS

CERN. They take part in the design, construction, and operation of the research infrastructures. CERN staff also contribute to the construction and operation of the experiments, as well as to the analysis of the data gathered for a vast community of users comprising over 12 500 scientists of 110 nationalities from institutes in more than 70 countries [35], [39]. Other personnel consists of associates, fellows, students and contractors.

Figure 3.2: Map of the region close to Geneva where the CERN site is located. The extent of the 27 km Large [40] Hadron Collider is indicated

The Organization's budget for the year 2021 is of the order of 1.347 billion Swiss francs [41]. Contributions are shared between the member states in proportion to their GNP: Germany, Italy, France and the United Kingdom are the main contributors. A number of major non-European nations participate in the LHC accelerator project having an observer status.

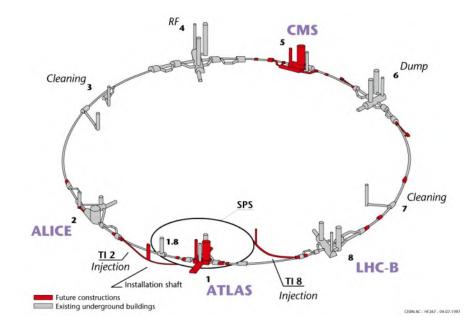

In the LHC experiments, ATLAS [2], CMS [3] and ALICE [4] and LHC-b (Figure 3.3), universities and research institutes from all over the world collaborate and contribute to the common effort either with in-kind services and equipment or by sharing costs directly with funds.

ALICE [4], "A Large Ion Collider Experiment", will observe proton and lead ion collisions in LHC. The experiment will study the physics of strongly interacting matter at extreme energy densities, where the formation of a new phase of matter, the quark-gluon plasma, is expected. ATLAS [43], "A Toroidal LHC Apparatus" and CMS, "The Compact Muon Solenoid" [44], look for the Higgs Boson [45], supersymmetry and aspects of heavy ion collisions. LHC-b [46], the LHC Beauty experiment, will make precision measurements of CP violation and rare decays [47].

Figure 3.3: The Large Hadron Collider and the experiments Atlas, CMS, LHC-b [42]

#### 3.1.1 Background

During the first half of the last century, European achievements and research dominated physics progress. After the Second World War, some of the leading physicists, Rabi, Amaldi, Auger and de Rougemont, realised, that only international co-operation could advance the science of physics and support the construction of new, powerful, expensive research facilities. The creation of a European high energy particle physics laboratory was recommended by a UNESCO meeting in Florence in 1950, and less than three years later a convention was signed by 12 countries creating the Conseil Européen pour la Recherche Nucléaire. Many important ideas and innovations in the accelerator domain have originated at CERN and were developed at machines such as the Intersecting Storage Rings (ISR), the Super Proton Synchrotron (SPS) and the Proton-Antiproton Collider (SppS). The first W and Z particles were produced at SppS, confirming the unified theory of electromagnetic and weak forces. The Large Electron-Positron Collider (LEP) tested extensively, with measurements unsurpassed in quantity and quality, the "Standard Model" [48]. The LEP data are very accurate and have sensitivity to phenomena that occur at energies beyond those of the machine itself, permitting a speculative "preview" of exciting potential new discoveries.

The evidence from LEP data analysis indicates that new physics should be discovered at centre-of-mass energies for proton-proton collisions around 1 TeV. The LHC has been designed for this search and it is now installed in the 27-kilometre tunnel. The LHC will be injected with beams coming from CERN's existing particle sources and accelerators. This reuse of existing installations has been the hallmark of CERN since its beginning and is one of the major reasons for the laboratory's success and longevity.

The LHC is a superconducting accelerator, by which is understood that the main bending and focussing magnet are built using superconducting technology. The main bending magnet has a field of 8.35 T at 7 TeV proton energy [49]. The LHC will be a versatile accelerator. It will accelerate proton beams to energies around 7 TeV collide them in beam crossing points, providing the experiments with high interaction rates. It will also be able to accelerate and bring into collision beams of heavy ions such as lead with a beam energy of 2.76 TeV/nucleon [50]. Colliding lead ions will yield a total centre-of-mass energy of  $2 \times 208 \times 2.76$  TeV = 1.15 PeV, about thirty times higher than the centre-of-mass energy available at the Relativistic Heavy Ion Collider Relativistic Heavy Ion Collider (RHIC) at the Brookhaven Laboratory in the US [51]. The LHC has been designed for theoretically predicted phenomena; however the machine is also built to offer possibly new discoveries not predicted by current theory [35].

#### 3.2 Physics motivation

Physics tries to give unified descriptions of the behaviour of matter and radiation. For a long time physicists considered matter to be constituted by fundamental particles and constructed an elaborate system of particle classification. The present "Standard Model" of particle physics sorts the elementary particles into three families, see Table 3.1. There are two quarks (and their antiparticles) and two leptons in each family: the "up" and "down" quarks, the electron and the electron-neutrino are in the first; the "strange" and the "charm" quark, the muon and the muon neutrino in the second; the "top" and the "bottom" quark, the tau and the tau neutrino in the third [52]. The Standard Model contains both fermionic and bosonic fundamental particles. Fermions are particles which possess half-integer spin and obey the Pauli exclusion principle, which states that no fermions can share the same quantum state. Bosons possess integer spin and do not obey the Pauli exclusion principle. Informally speaking, fermions are particles of matter and bosons are particles that transmit forces [48].

| Generation 1 (ordinary matter) |                        |                 |                        |

|--------------------------------|------------------------|-----------------|------------------------|

| Fermion (Left -handed)         | Symbol                 | Electric charge | Mas                    |

| Electron                       | е                      | -1              | $0.511 { m MeV}$       |

| Electron neutrino              | Ve                     | 0               | < 50  eV               |

| Positron                       | $e^c$                  | +1              | $0.511 { m MeV}$       |

| Electron antineutrino          | $\mathbf{v}_e^c$       | 0               | < 50  eV               |

| Up quark                       | u                      | +2/3            | $\sim 5 \text{ MeV}$   |

| Down quark                     | d                      | -1/3            | $\sim 10 \text{ MeV}$  |

| Anti-up antiquark              | u <sup>c</sup>         | -2/3            | $\sim 5 \text{ MeV}$   |

| Anti-down antiquark            | $d^c$                  | +1/3            | $\sim 10 { m MeV}$     |

|                                | Generati               | on 2            |                        |

| Muon                           | $\mu$                  | 1               | $105.6~{\rm MeV}$      |

| Muon neutrino                  | $v_{\mu}$              | 0               | $< 0.5 {\rm MeV}$      |

| Anti-Muon                      | $\mu^{c}$              | +1              | $105.6~{\rm MeV}$      |

| Muon antineutrino              | $\mathrm{V}^{\mu}_{c}$ | 0               | < 0.5  MeV             |

| Charm quark                    | с                      | +2/3            | $\sim 1.5 \text{ GeV}$ |

| Strange quark                  | s                      | -1/3            | $\sim 100 \text{ MeV}$ |

| Anti-charm antiquark           | $c^c$                  | -2/3            | $\sim 1.5 \text{ GeV}$ |

| Anti-strange antiquark         | $s^c$                  | +1/3            | $\sim 100 \text{ MeV}$ |

|                                | Generatio              | on 3            |                        |

| Tau lepton                     | $\tau$                 | -1              | $1.784 \mathrm{GeV}$   |

| Tau neutrino                   | $V_{\tau}$             | 0               | $< 70 { m MeV}$        |

| Anti-Tau                       | $\tau^c$               | +1              | $1.784 \mathrm{GeV}$   |

| Tau antineutrino               | $\mathbf{V}_c^{\tau}$  | 0               | $< 70 {\rm MeV}$       |

| Top quark                      | t                      | +2/3            | $173 { m GeV}$         |

| Bottom quark                   | b                      | -1/3            | $\sim 4.7 \text{ GeV}$ |

| Anti-top antiquark             | t <sup>c</sup>         | -2/3            | $173 { m GeV}$         |

| Anti-bottom antiquark          | $\mathbf{b}^{c}$       | +1/3            | $\sim 4.7 \text{ GeV}$ |

Table 3.1: Fermions: leptons and quarks [35].

In the Standard Model, the theory of the electroweak interaction (which describes the weak and electromagnetic interactions) the forces between fermions are modeled by coupling them to bosons which mediate (or "carry") the forces [53]. The bosons in the "Standard Model" are:

- Photons, which mediate the electromagnetic interaction.

- W and Z bosons, which mediate the weak electromagnetic force (discovered at CERN).

- Eight species of gluons, which mediate the strong nuclear force.

- The Higgs bosons, which are thought to be responsible for the existence of inertial mass [54], [55].

#### **3.2.1** Higher and higher energies